工業控制

Microchip LAN9252 2-3端口EtherCAT控制器解決方案

microchip公司的LAN9252是集成了兩路以太網PHY的2/3端口EtherCAT從控制器,包括了全雙工100BASE-TX收發器和支持100Mbps (100BASE-TX),支持3個Fieldbus存儲器管理單元(FMMU)和4個SyncManagers,主要用在馬達控制,過程/工廠自動化,通信模塊,接口卡,傳感器,水和氣動閥門系統等.本文介紹了AN9252產品亮點和主要優勢, 系統框圖和內部框圖, 工作模式圖和電源連接圖,以及評估板EVB-LAN9252-HBI-SPI-SQI-GPIO EtherCAT? HBI/SPI+GPIO主要特性,框圖,電路圖和材料清單.

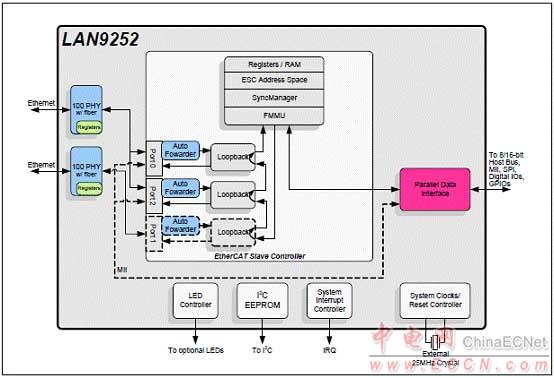

The LAN9252 is a 2/3-port EtherCAT slave controller with dual integrated Ethernet PHYs which each contain a fullduplex 100BASE-TX transceiver and support 100Mbps (100BASE-TX) operation. The LAN9252 supports HP Auto-MDIX, allowing the use of direct connect or cross-over LAN cables. 100BASE-FX is supported via an external fiber transceiver.

The LAN9252 includes an EtherCAT slave controller with 4K bytes of Dual Port memory (DPRAM) and 3 Fieldbus Memory Management Units (FMMUs). Each FMMU performs the task of mapping logical addresses to physical addresses.

The EtherCAT slave controller also includes 4 SyncManagers to allow the exchange of data between the EtherCAT master and the local application. Each SyncManager’s direction and mode of operation is configured by the EtherCAT master.

Two modes of operation are available: buffered mode or mailbox mode. In the buffered mode, both the local microcontroller and EtherCAT master can write to the device concurrently. The buffer within the LAN9252 will always contain the latest data. If newer data arrives before the old data can be read out, the old data will be dropped. In mailbox mode, access to the buffer by the local microcontroller and the EtherCAT master is performed using handshakes, guaranteeing that no data will be dropped.

Two user selectable host bus interface options are available:

? Indexed register access

This implementation provides three index/data register banks, each with independent Byte/WORD to DWORD conversion. Internal registers are accessed by first writing one of the three index registers, followed by reading or writing the corresponding data register. Three index/data register banks support up to 3 independent driver threads without access conflicts. Each thread can write its assigned index register without the issue of anotherthread overwriting it. Two 16-bit cycles or four 8-bit cycles are required within the same 32-bit index/data register -however, these access can be interleaved. Direct (non-indexed) read and write accesses are supported to the process data FIFOs. The direct FIFO access provides independent Byte/WORD to DWORD conversion, supporting interleaved accesses with the index/data registers.

? Multiplexed address/data bus

This implementation provides a multiplexed address and data bus with both single phase and dual phase address support. The address is loaded with an address strobe followed by data access using a read or write strobe. Two back to back 16-bit data cycles or 4 back to back 8-bit data cycles are required within the same 32-bit DWORD.

These accesses must be sequential without any interleaved accesses to other registers. Burst read and write accesses are supported to the process data FIFOs by performing one address cycle followed by multiple read or write data cycles.

The HBI supports 8/16-bit operation with big, little, and mixed endian operations. Two process data RAM FIFOs interface the HBI to the EtherCAT slave controller and facilitate the transferring of process data information between the host CPU and the EtherCAT slave. A configurable host interrupt pin allows the device to inform the host CPU of any internal interrupts.

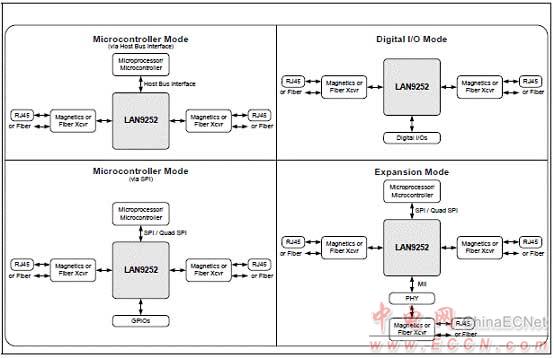

An SPI / Quad SPI slave controller provides a low pin count synchronous slave interface that facilitates communication between the device and a host system. The SPI / Quad SPI slave allows access to the System CSRs, internal FIFOs and memories. It supports single and multiple register read and write commands with incrementing, decrementing and static addressing. Single, Dual and Quad bit lanes are supported with a clock rate of up to 80 MHz.

The LAN9252 supports numerous power management and wakeup features. The LAN9252 can be placed in a reduced power mode and can be programmed to issue an external wake signal (IRQ) via several methods, including “Magic Packet”, “Wake on LAN”, wake on broadcast, wake on perfect DA, and “Link Status Change”. This signal is ideal for triggering system power-up using remote Ethernet wakeup events. The device can be removed from the low power state via a host processor command or one of the wake events.

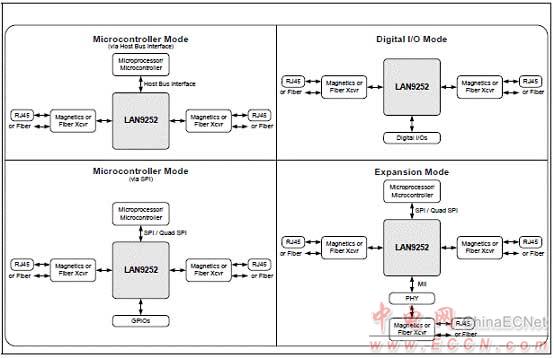

For simple digital modules without microcontrollers, the LAN9252 can also operate in Digital I/O Mode where 16 digital signals can be controlled or monitored by the EtherCAT master.

To enable star or tree network topologies, the device can be configured as a 3-port slave, providing an additional MII port. This port can be connected to an external PHY, forming a tap along the current daisy chain, or to another LAN9252 creating a 4-port solution. The MII port can point upstream (as Port 0) or downstream (as Port 2).

LED support consists of a standard RUN indicator and a LINK / Activity indicator per port. A 64-bit distributed clock is included to enable high-precision synchronization and to provide accurate information about the local timing of data acquisition.

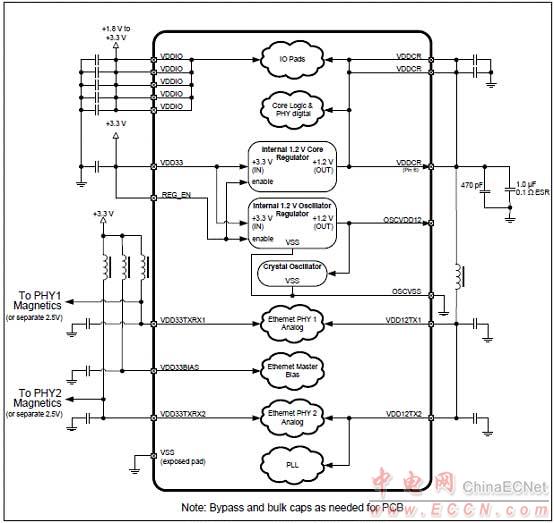

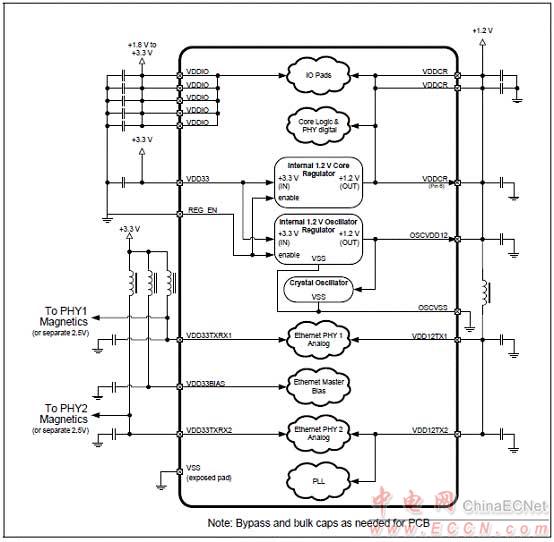

The LAN9252 can be configured to operate via a single 3.3V supply utilizing an integrated 3.3V to 1.2V linear regulator.

The linear regulator may be optionally disabled, allowing usage of a high efficiency external regulator for lower system power dissipation.

LAN9252亮點:

? 2/3-port EtherCAT slave controller with 3 Fieldbus Memory Management Units (FMMUs) and

4 SyncManagers

? Interfaces to most 8/16-bit embedded controllers and 32-bit embedded controllers with an 8/16-bit bus

? Integrated Ethernet PHYs with HP Auto-MDIX

? Wake on LAN (WoL) support

? Low power mode allows systems to enter sleep mode until addressed by the Master

? Cable diagnostic support

? 1.8V to 3.3V variable voltage I/O

? Integrated 1.2V regulator for single 3.3V operation

? Low pin count and small body size package

LAN9252主要優勢:

? Integrated high-performance 100Mbps Ethernet transceivers

- Compliant with IEEE 802.3/802.3u (Fast Ethernet)

- 100BASE-FX support via external fiber transceiver

- Loop-back modes

- Automatic polarity detection and correction

- HP Auto-MDIX

? EtherCAT slave controller

- Supports 3 FMMUs

- Supports 4 SyncManagers

- Distributed clock support allows synchronization with other EtherCAT devices

- 4K bytes of DPRAM

? 8/16-Bit Host Bus Interface

- Indexed register or multiplexed bus

- Allows local host to enter sleep mode until addressed by EtherCAT Master

- SPI / Quad SPI support

? Digital I/O Mode for optimized system cost

? 3rd port for flexible network configurations

? Comprehensive power management features

- 3 power-down levels

- Wake on link status change (energy detect)

- Magic packet wakeup, Wake on LAN (WoL), wake on broadcast, wake on perfect DA

- Wakeup indicator event signal

? Power and I/O

- Integrated power-on reset circuit

- Latch-up performance exceeds 150mA per EIA/JESD78, Class II

- JEDEC Class 3A ESD performance

- Single 3.3V power supply (integrated 1.2V regulator)

? Additional Features

- Multifunction GPIOs

- Ability to use low cost 25MHz crystal for reduced BOM

? Packaging

- Pb-free RoHS compliant 64-pin QFN or 64-pin TQFPEP

? Available in commercial, industrial, and extended industrial* temp. ranges

LAN9252目標應用:

? Motor Motion Control

? Process/Factory Automation

? Communication Modules, Interface Cards

? Sensors

? Hydraulic & Pneumatic Valve Systems

? Operator Interfaces

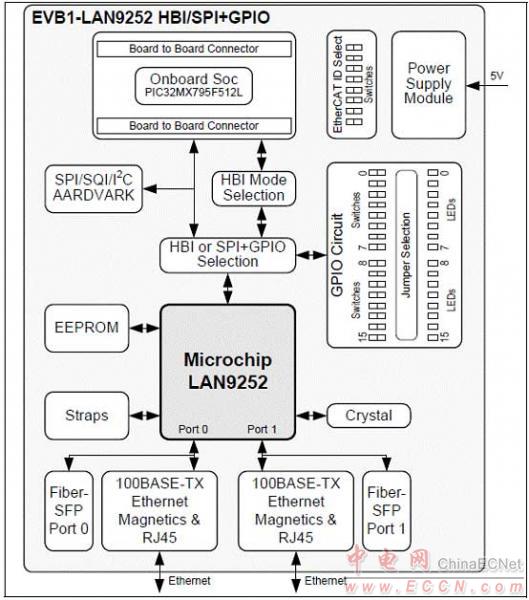

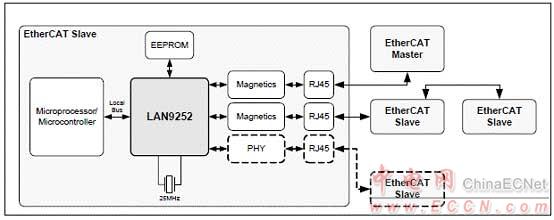

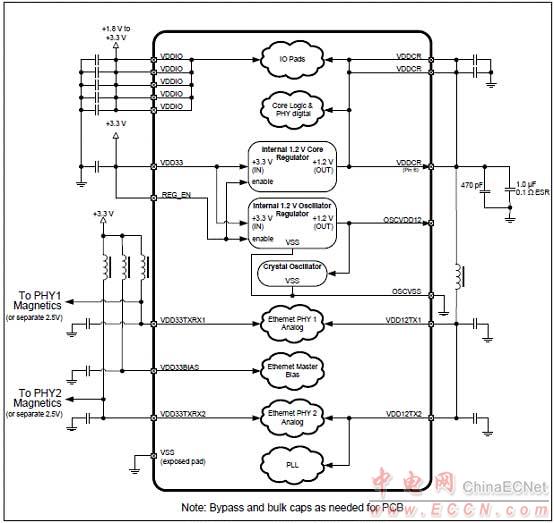

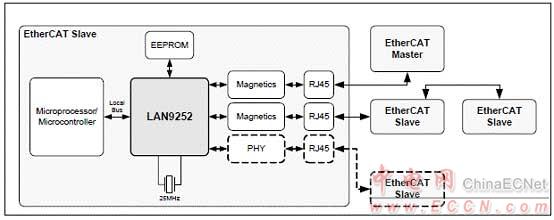

圖1. LAN9252系統框圖

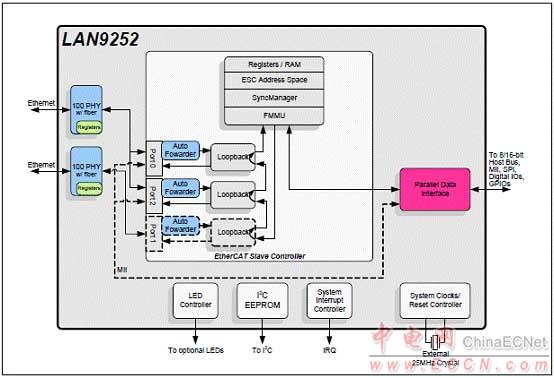

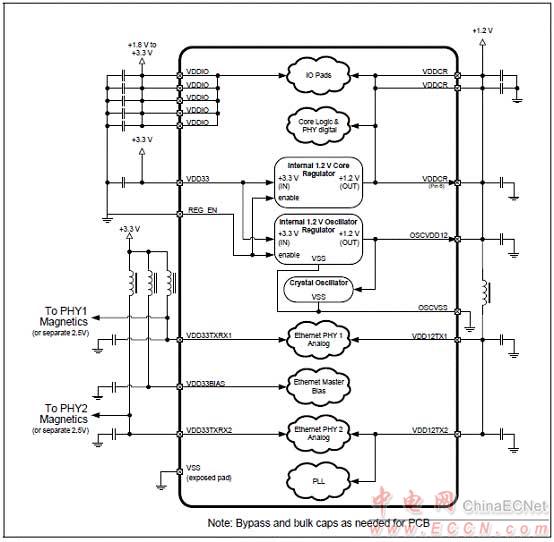

圖2. LAN9252內部框圖

圖3. LAN9252工作模式圖

圖4. LAN9252電源連接圖-穩壓器使能

圖5. LAN9252電源連接圖-穩壓器不能

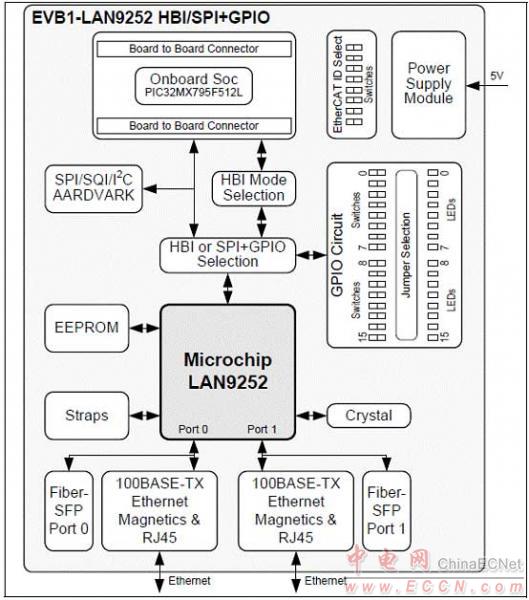

評估板EVB-LAN9252-HBI-SPI-SQI-GPIO EtherCAT? HBI/SPI+GPIO

The LAN9252 is a 2-port EtherCAT? Slave Controller (ESC) with dual integrated Ethernet PHYs which each contain a full-duplex 100BASE-TX transceiver and support 100Mbps (100BASE-TX) operation. 100BASE-FX is supported via an external fiber transceiver.

Each port receives an EtherCAT? frame, performs frame checking and forwards it to the next port. Time stamps of received frames are generated when they are received.

The Loop-back function of each port forwards the frames to the next logical port if there is either no link at a port, if the port is not available, or if the loop is closed for that port.

The Loop-back function of port 0 forwards the frames to the EtherCAT? Processing Unit. The loop settings can be controlled by the EtherCAT? master.

Packets are forwarded in the following order:

Port 0 -> EtherCAT? Processing Unit -> Port 1 -> Port 2.

The EtherCAT? Processing Unit (EPU) receives, analyzes and processes the Ether-CAT? data stream. The main purpose of the EtherCAT? Processing unit is to enable and coordinate access to the internal registers and the memory space of the ESC, which can be addressed both from the EtherCAT? master and from the local application.

Data exchange between master and slave applications is comparable to a dual-ported memory (process memory), enhanced by special functions for consistency checking (SyncManager) and data mapping (FMMU). Each FMMU performs bitwise mapping of logical EtherCAT? system addresses to physical device addresses.

The scope of this document is to describe the EVB-LAN9252-HBI-SPI-SQI-GPIO setup, which supports a HBI/SPI+GPIO Interface and corresponding jumper configurations. The LAN9252 is connected to an RJ45 Ethernet jack with integrated magnetic for 100BASE-TX connectivity.

評估板EVB-LAN9252-HBI-SPI-SQI-GPIO EtherCAT? HBI/SPI+GPIO